## 2 Ampere Single Low-Side Ultrafast MOSFET Drivers

#### **Features**

- Built using the advantages and compatibility of CMOS and IXYS HDMOS™ processes

- Latch-Up Protected up to 2 Amps

- High 2A Peak Output Current

- Wide Operating Range: 4.5V to 25V

- -55°C to +125°C Extended Operating Temperature

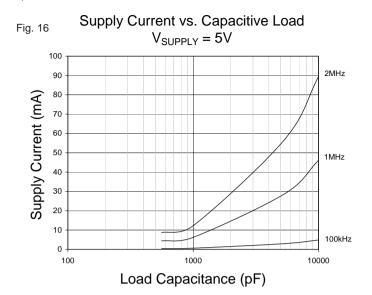

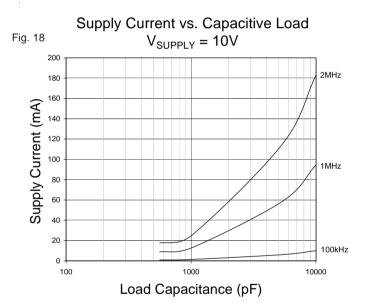

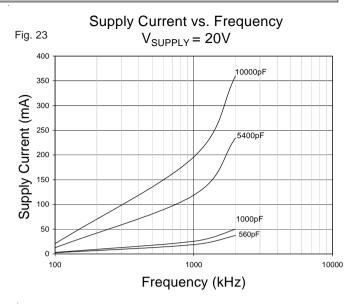

- High Capacitive Load Drive Capability: 1000pF in <10ns</li>

- · Matched Rise And Fall Times

- Low Propagation Delay Time

- Low Output Impedance

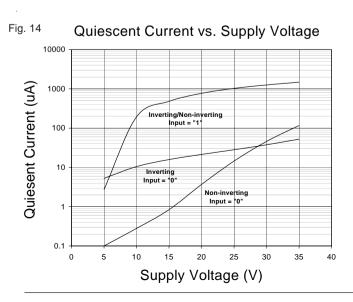

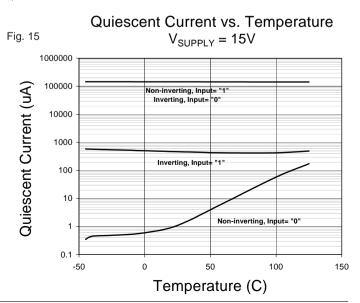

- Low Supply Current

### **Applications**

- Driving MOSFETs and IGBTs

- Motor Controls

- Line Drivers

- · Pulse Generators

- Local Power ON/OFF Switch

- Switch Mode Power Supplies (SMPS)

- DC to DC Converters

- Pulse Transformer Driver

- Class D Switching Amplifiers

- Power Charge Pumps

### **General Description**

The IXDR502, and IXDS502 each consist of a single 2A CMOS high speed gate driver for driving the latest IXYS MOSFETs & IGBTs. Each type can source and sink 2 Amps of peak current while producing voltage rise and fall times of less than 15ns. The input of each driver is TTL or CMOS compatible and is virtually immune to latch up. Patented\* design innovations eliminate cross conduction and current "shoot-through". Improved speed and drive capabilities are further enhanced by very quick & matched rise and fall times.

The IXDR502 is configured as a single inverting gate driver, and the IXDS502 is configured as a single non-inverting gate driver.

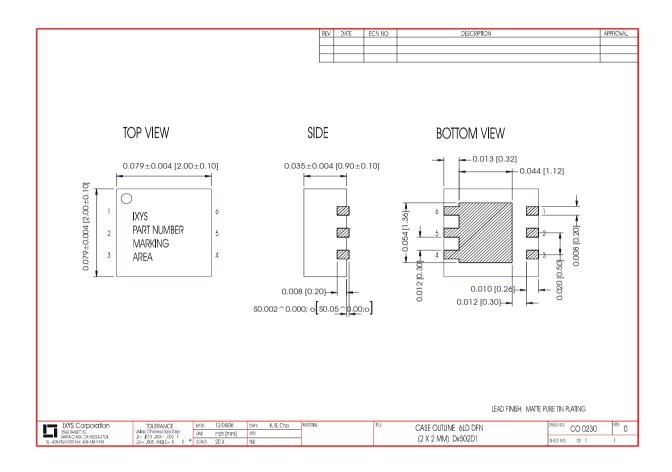

The IXDR502, and IXDS502 are available in the 6-Lead DFN (D1) package, which occupies less than 20% of the board area of a typical 8-Pin SOIC package.

\*United States Patent 6,917,227

### **Ordering Information**

| Part Number   | Description                  | Package<br>Type | Packing Style       | Pack<br>Qty | Configuration    |

|---------------|------------------------------|-----------------|---------------------|-------------|------------------|

| IXDR502D1B    | 2A Low Side Gate Driver I.C. | 6-Lead DFN      | 2" x 2" Waffle Pack | 121         | Single Inverting |

| IXDR502D1BT/R | 2A Low Side Gate Driver I.C. | 6-Lead DFN      | 7" Tape and Reel    | 2500        | Driver           |

| IXDS502D1B    | 2A Low Side Gate Driver I.C. | 6-Lead DFN      | 2" x 2" Waffle Pack | 121         | Single Non-      |

| IXDS502D1BT/R | 2A Low Side Gate Driver I.C. | 6-Lead DFN      | 7" Tape and Reel    | 2500        | Inverting Driver |

NOTE: All parts are lead-free and RoHS Compliant

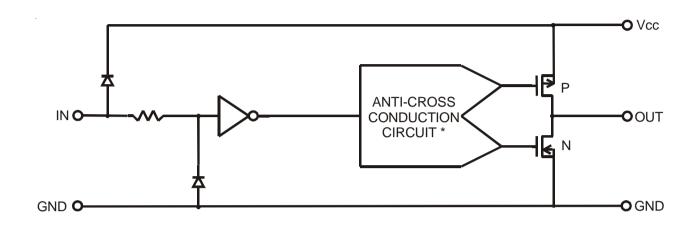

Figure 1 - IXDS502 Non-Inverting 2A Gate Driver Functional Block Diagram

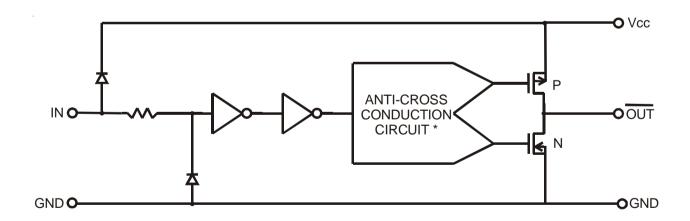

Figure 2 - IXDR502 Inverting 2A Gate Driver Functional Block Diagram

<sup>\*</sup> United States Patent 6,917,227

## Absolute Maximum Ratings (1)

| Parameter                 | Value                            |

|---------------------------|----------------------------------|

| Supply Voltage            | 35V                              |

| All Other Pins            | -0.3 V to V <sub>cc</sub> + 0.3V |

| Junction Temperature      | 150 °C                           |

| Storage Temperature       | -65 °C to 150 °C                 |

| Lead Temperature (10 Sec) | 300 °C                           |

# Operating Ratings (2)

| Parameter        |            |                         | Value        |

|------------------|------------|-------------------------|--------------|

| Operating Supply |            | 4.5V to 25V             |              |

| Operating Tempe  | ange       | -55 °C to 125 °C        |              |

| Package Therma   | l Resistar | nce *                   |              |

| 6-Lead DFN       | (D1)       | $\theta_{L\Delta}(typ)$ | 125-200 °C/W |

| 6-Lead DFN       | (D1)       |                         | )3.3 °C/W    |

| 6-Lead DFN       | (D1)       |                         | 7.3 °C/W     |

# Electrical Characteristics @ $T_A = 25$ °C $^{(3)}$

Unless otherwise noted,  $4.5V \le V_{CC} \le 25V$  .

All voltage measurements with respect to GND. IXD\_502 configured as described in Test Conditions.

| Symbol              | Parameter Test Conditions    |                                                                | Min                     | Ту <b>р</b> <sup>(4)</sup> | Max                   | Units    |  |

|---------------------|------------------------------|----------------------------------------------------------------|-------------------------|----------------------------|-----------------------|----------|--|

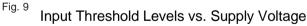

| V <sub>IH</sub>     | High input voltage           | $4.5V \le V_{CC} \le 18V$                                      | 2.5                     |                            |                       | V        |  |

| V <sub>IL</sub>     | Low input voltage            | $4.5V \le V_{CC} \le 18V$                                      |                         |                            | 1.0                   | V        |  |

| V <sub>IN</sub>     | Input voltage range          |                                                                | -5                      |                            | V <sub>CC</sub> + 0.3 | V        |  |

| I <sub>IN</sub>     | Input current                | $0V \le V_{IN} \le V_{CC}$                                     | -10                     |                            | 10                    | μΑ       |  |

| V <sub>OH</sub>     | High output voltage          |                                                                | V <sub>CC</sub> - 0.025 |                            |                       | V        |  |

| V <sub>OL</sub>     | Low output voltage           |                                                                |                         |                            | 0.025                 | V        |  |

| R <sub>OH</sub>     | High state output resistance | V <sub>CC</sub> = 15V                                          |                         | 3                          | 4                     | Ω        |  |

| R <sub>OL</sub>     | Low state output resistance  | V <sub>CC</sub> = 15V                                          |                         | 2.2                        | 3                     | Ω        |  |

| I <sub>PEAK</sub>   | Peak output current          | V <sub>CC</sub> = 15V                                          |                         | 2                          |                       | Α        |  |

| I <sub>DC</sub>     | Continuous output current    |                                                                |                         |                            | 0.5                   | Α        |  |

| t <sub>R</sub>      | Rise time                    | $C_{LOAD} = 1000pF V_{CC} = 15V$                               |                         | 7.5                        | 12                    | ns       |  |

| t <sub>F</sub>      | Fall time                    | $C_{LOAD} = 1000pF V_{CC} = 15V$                               |                         | 6.5                        | 10                    | ns       |  |

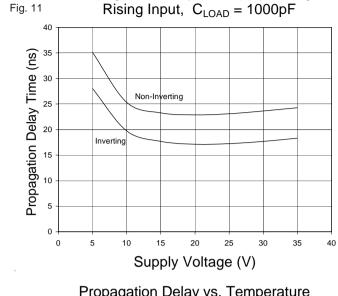

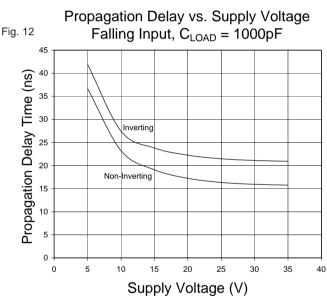

| t <sub>ONDLY</sub>  | ON propagation delay         | C <sub>LOAD</sub> = 1000pF V <sub>CC</sub> = 15V               |                         | 25                         | 35                    | ns       |  |

| t <sub>OFFDLY</sub> | OFF propagation delay        | $C_{LOAD} = 1000pF V_{CC} = 15V$                               |                         | 20                         | 30                    | ns       |  |

| V <sub>CC</sub>     | Power supply voltage         |                                                                | 4.5                     | 15                         | 25                    | V        |  |

| I <sub>CC</sub>     | D                            | $V_{IN} = 3.5V$                                                |                         | 1                          | 2                     | mA       |  |

|                     | Power supply current         | $V_{IN} = 0V$<br>$V_{IN} = +V_{CC}, (4.5V \le V_{CC} \le 18V)$ |                         | 0                          | 15<br>15              | μΑ<br>μΑ |  |

### Electrical Characteristics @ temperatures over -55 °C to 125 °C (3)

Unless otherwise noted,  $4.5V \le V_{\rm CC} \le 22V$  , Tj < 150°C

All voltage measurements with respect to GND. IXD\_502 configured as described in Test Conditions.

| Symbol              | Parameter                          | Test Conditions                                                | Min                    | Тур | Max                   | Units |

|---------------------|------------------------------------|----------------------------------------------------------------|------------------------|-----|-----------------------|-------|

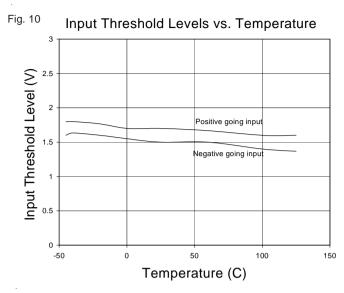

| V <sub>IH</sub>     | High input voltage                 | $4.5V \le V_{CC} \le 15V$                                      | 3.5                    |     |                       | V     |

| V <sub>IL</sub>     | Low input voltage                  | $4.5V \le V_{CC} \le 15V$                                      |                        |     | 0.8                   | V     |

| V <sub>IN</sub>     | Input voltage range                |                                                                | -5                     |     | V <sub>CC</sub> + 0.3 | V     |

| I <sub>IN</sub>     | Input current                      | $0V \le V_{IN} \le V_{CC}$                                     | -20                    |     | 20                    | μΑ    |

| V <sub>OH</sub>     | High output voltage                |                                                                | V <sub>CC</sub> - 0.05 |     |                       | V     |

| V <sub>OL</sub>     | Low output voltage                 |                                                                |                        |     | 0.05                  | V     |

| R <sub>OH</sub>     | Output resistance<br>@ Output high | V <sub>CC</sub> = 15V                                          |                        |     | 6                     | Ω     |

| R <sub>OL</sub>     | Output resistance  @ Output Low    | V <sub>CC</sub> = 15V                                          |                        |     | 4                     | Ω     |

| I <sub>DC</sub>     | Continuous output current          |                                                                |                        |     | 0.3                   | Α     |

| t <sub>R</sub>      | Rise time                          | C <sub>L</sub> =1000pF Vcc=15V                                 |                        |     | 14                    | ns    |

| t <sub>F</sub>      | Fall time                          | C <sub>L</sub> =1000pF Vcc=15V                                 |                        |     | 12                    | ns    |

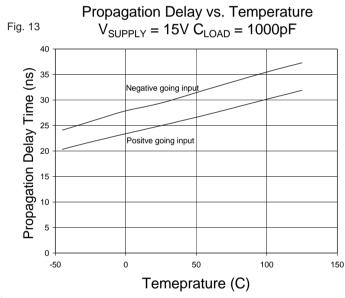

| t <sub>ONDLY</sub>  | On-time propagation delay          | C <sub>L</sub> =1000pF Vcc=15V                                 |                        |     | 40                    | ns    |

| t <sub>OFFDLY</sub> | Off-time propagation delay         | C <sub>L</sub> =1000pF Vcc=15V                                 |                        |     | 35                    | ns    |

| V <sub>CC</sub>     | Power supply voltage               |                                                                | 4.5                    | 15  | 22                    | V     |

| I <sub>CC</sub>     | Power supply current               | $V_{IN} = 3.5V$                                                |                        | 1   | 3                     | mA    |

|                     |                                    | $V_{IN} = 0V$                                                  |                        | 0   | 10                    | μΑ    |

|                     |                                    | $V_{IN} = + V_{CC}, (4.5 \text{V} \le V_{CC} \le 18 \text{V})$ |                        |     | 10                    | μΑ    |

#### Notes:

- 1. Operating the device beyond the parameters listed as "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

- 2. The device is not intended to be operated outside of the Operating Ratings.

- 3. Electrical Characteristics provided are associated with the stated Test Conditions.

- 4. Typical values are presented in order to communicate how the device is expected to perform, but not necessarily to highlight any specific performance limits within which the device is guaranteed to function.

- 1) The  $\theta_{J,A}$  (typ) is defined as junction to ambient. The  $\theta_{J,A}$  of the standard single die 8-Lead PDIP and 8-Lead SOIC are dominated by the resistance of the package, and the IXD\_5XX are typical. The values for these packages are natural convection values with vertical boards and the values would be lower with forced convection. For the 6-Lead DFN package, the  $\theta_{J,A}$  value supposes the DFN package is soldered on a PCB. The  $\theta_{J,A}$  (typ) is 200 °C/W with no special provisions on the PCB, but because the center pad provides a low thermal resistance to the die, it is easy to reduce the  $\theta_{J,A}$  by adding connected copper pads or traces on the PCB. These can reduce the  $\theta_{J,A}$  (typ) to 125 °C/W easily, and potentially even lower. The  $\theta_{J,A}$  for DFN on PCB without heatsink or thermal management will vary significantly with size, construction, layout, materials, etc. This typical range tells the user what they are likely to get if no thermal management is done.

- 2)  $\theta_{J\cdot C}$  (max) is defined as juction to case, where case is the large pad on the back of the DFN package. The  $\theta_{J\cdot C}$  values are generally not published for the PDIP and SOIC packages. The  $\theta_{J\cdot C}$  for the DFN packages are important to show the low thermal resistance from junction to the die attach pad on the back of the DFN, -- and a guardband has been added to be safe.

- 3) The  $\theta_{JS}$  (typ) is defined as junction to heatsink, where the DFN package is soldered to a thermal substrate that is mounted on a heatsink. The value must be typical because there are a variety of thermal substrates. This value was calculated based on easily available IMS in the U.S. or Europe, and not a premium Japanese IMS. A 4 mil dialectric with a thermal conductivity of 2.2W/mC was assumed. The result was given as typical, and indicates what a user would expect on a typical IMS substrate, and shows the potential low thermal resistance for the DFN package.

<sup>\*</sup> The following notes are meant to define the conditions for the  $\theta_{J-A}$ ,  $\theta_{J-C}$  and  $\theta_{J-S}$  values:

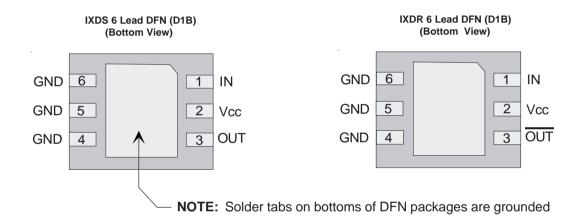

### **Pin Description**

| PIN NUMBER | SYMBOL | FUNCTION       | DESCRIPTION                                                                                                                                                                                                           |

|------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | IN     | Signal Input   | Input signal-TTL or CMOS compatible.                                                                                                                                                                                  |

| 2          | Vcc    | Supply Voltage | Positive power supply voltage input. This pin provides power to the entire chip. The range for this voltage is from 4.5V to 25V.                                                                                      |

| 3          | OUT    | Drive Output   | Driver output. For application purposes, this pin is connected via a resistor to the gate of a MOSFET or IGBT.                                                                                                        |

| 4,5,6      | GND    | Ground         | The drivers ground pins. Internally connected to all circuitry, these pins provide ground reference for the entire device. These pins should be connected to a low noise analog ground plane for optimum performance. |

CAUTION: Follow proper ESD procedures when handling and assembling this component.

## **Pin Configuration**

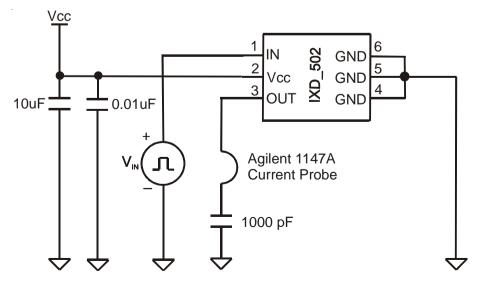

Figure 3 - Characteristics Test Diagram

IXYS reserves the right to change limits, test conditions, and dimensions.

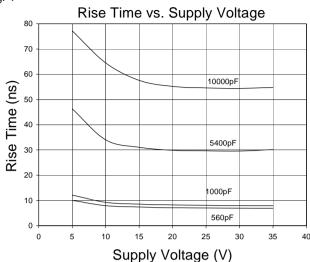

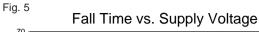

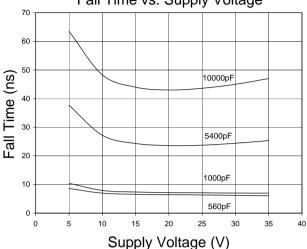

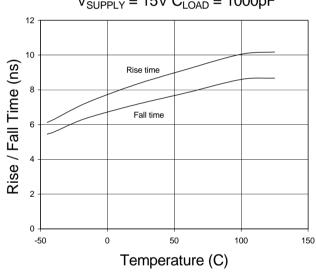

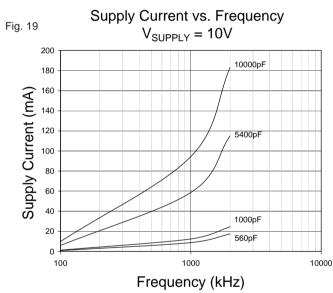

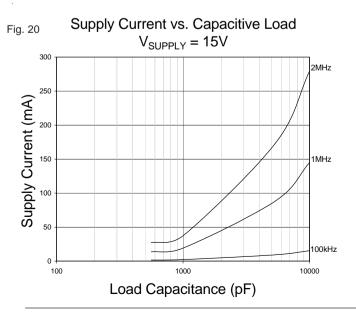

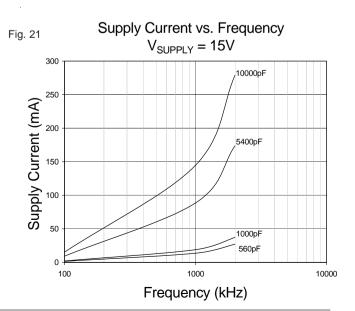

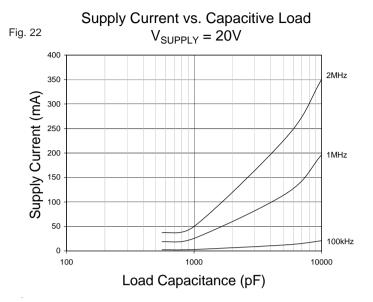

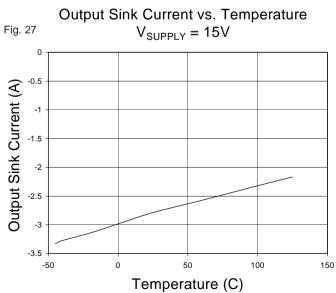

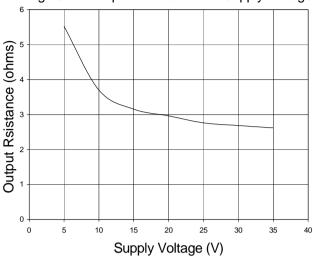

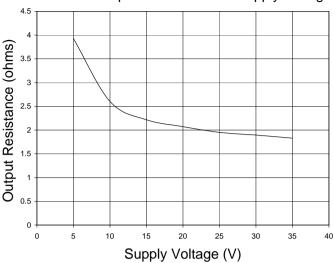

## **Typical Performance Characteristics**

#### Rise / Fall Time vs. Temperature Fig. 6 $V_{SUPPLY} = 15V C_{LOAD} = 1000pF$

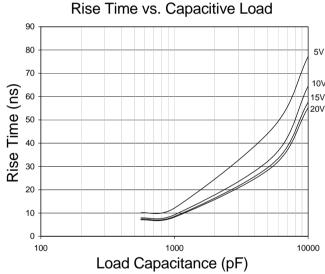

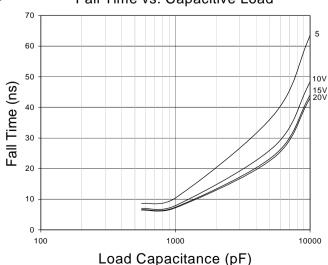

# Fig. 7

#### Fig. 8 Fall Time vs. Capacitive Load

Propagation Delay vs. Supply Voltage

8

Fig. 28 High State Output Resistance vs. Supply Voltage

Fig. 29 Low State Output Resistance vs. Supply Voltage

#### Supply Bypassing, Grounding Practices And Output Lead Inductance

When designing a circuit to drive a high speed MOSFET utilizing the IXD\_502, it is very important to observe certain design criteria in order to optimize performance of the driver. Particular attention needs to be paid to **Supply Bypassing**, **Grounding**, and minimizing the **Output Lead Inductance**.

Say, for example, we are using the IXD\_502 to charge a 1500pF capacitive load from 0 to 25 volts in 25ns.

Using the formula: I=  $\Delta V$  C /  $\Delta t$ , where  $\Delta V$ =25V C=1500pF &  $\Delta t$ =25ns, we can determine that to charge 1500pF to 25 volts in 25ns will take a constant current of 1.5A. (In reality, the charging current won't be constant, and will peak somewhere around 2A).

#### SUPPLY BYPASSING

In order for our design to turn the load on properly, the IXD\_502 must be able to draw this 1.5A of current from the power supply in the 25ns. This means that there must be very low impedance between the driver and the power supply. The most common method of achieving this low impedance is to bypass the power supply at the driver with a capacitance value that is an order of magnitude larger than the load capacitance. Usually, this would be achieved by placing two different types of bypassing capacitors, with complementary impedance curves, very close to the driver itself. (These capacitors should be carefully selected and should have low inductance, low resistance and high-pulse current-service ratings). Lead lengths may radiate at high frequency due to inductance, so care should be taken to keep the lengths of the leads between these bypass capacitors and the IXD\_502 to an absolute minimum.

#### **GROUNDING**

In order for the design to turn the load off properly, the IXD\_502 must be able to drain this 1.5A of current into an adequate grounding system. There are three paths for returning current that need to be considered: Path #1 is between the IXD\_502 and its load. Path #2 is between the IXD\_502 and its power supply. Path #3 is between the IXD\_502 and whatever logic is driving it. All three of these paths should be as low in resistance and inductance as possible, and thus as short as practical. In addition, every effort should be made to keep these three ground paths distinctly separate. Otherwise, the returning ground current from the load may develop a voltage that would have a detrimental effect on the logic line driving the IXD\_502.

#### **OUTPUT LEAD INDUCTANCE**

Of equal importance to Supply Bypassing and Grounding are issues related to the Output Lead Inductance. Every effort should be made to keep the leads between the driver and its load as short and wide as possible. If the driver must be placed farther than 2" (5mm) from the load, then the output leads should be treated as transmission lines. In this case, a twisted-pair should be considered, and the return line of each twisted pair should be placed as close as possible to the ground pin of the driver, and connected directly to the ground terminal of the load.

IXYS Corporation 3540 Bassett St; Santa Clara, CA 95054 Tel: 408-982-0700; Fax: 408-496-0670

e-mail: sales@ixys.net

www.ixys.com

IXYS Semiconductor GmbH Edisonstrasse15; D-68623; Lampertheim Tel: +49-6206-503-0; Fax: +49-6206-503627 e-mail: marcom@ixys.de